摘 要

数字信号处理在科学和工程技术许多领域中得到广泛的应用,与FIR数字滤波器相比,IIR数字滤波器可以用较低的阶数获得较高的选择性,故本课题采用一种基于FPGA的IIR数字滤波器的设计方案,首先分析了IIR数字滤波器的原理及设计方法,然后通过MAX+PLUSⅡ的设计平台,采用自顶向下的模块化设计思想将整个IIR数字滤波器分为:时序控制、延时、补码乘加和累加四个功能模块。分别对各模块采用VHDL进行描述后,进行了仿真和综合。仿真结果表明,本课题所设计的IIR数字滤波器运算速度较快,系数改变灵活,有较好的参考价值。

关键词:电子设计自动化; IIR数字滤波器; 现场可编程门阵列; 硬件描述语言

The design for IIR digital filter based on FPGA

Abstract

Digital signal processing is widely used in lots of fields, such as in science and project technique. Compared with FIR digital filter, IIR digital filter can get high selectivity with low factorial. A kind of IIR digital filter design method was introduced in the paper, which is based on FPGA. By used the design plant of MAX+PLUSⅡ, we adopt blocking method named “Top-down ” and divide the entire IIR digital filter into four blocks, which are Clock control, Time delay, Multiply-addition and Progression. After described with VHDL, we do emulate and synthesis to each block. The result shows that, the introduced IIR digital filter runs fast, and the coefficient changes agility. It has high worth for consulting.

Key Words:Electronic Design Automation; IIR Digital Filter; Field Programmable Gate Array; very High Speed Integrated Circuit Hardware Description Language (VHDL)

IIR数字滤波器概念

数字滤波器是完成信号滤波处理功能的,用有限精度算法实现的离散时间线性非时变系统[2]。输入一组数字量,通过运算输出的是另一组数字量。数字滤波器具有稳定性好、精度高、灵活性大等突出优点。随着数字技术的发展,用数字技术设计滤波器的功能越来越受到人们的注意和广泛的应用。

目 录 11000字

摘 要 I

Abstract II

引 言 1

1 IIR数字滤波器及其硬件实现方法 2

1.1 IIR数字滤波器概念 2

1.1.1 IIR数字滤波器的原理 2

1.1.2 IIR数字滤波器的基本结构 2

1.1.3 IIR数字滤波器的设计方法 3

1.2 IIR数字滤波器的硬件实现方案 3

2 EDA技术和可编程逻辑器件 8

2.1 电子设计自动化EDA技术 8

2.2 可编程逻辑器件 8

2.2.1 可编程逻辑器件简介 8

2.2.2 使用FPGA器件进行开发的优点 9

2.2.3 FPGA设计的开发流程 9

2.3 硬件描述语言VHDL及数字系统设计方法 10

2.3.1 硬件描述语言VHDL简介 10

2.3.2利用VHDL设计数字系统 10

(毕业设计)

3 IIR数字滤波器的设计与仿真结果分析 11

3.1 各模块的设计与仿真结果分析 11

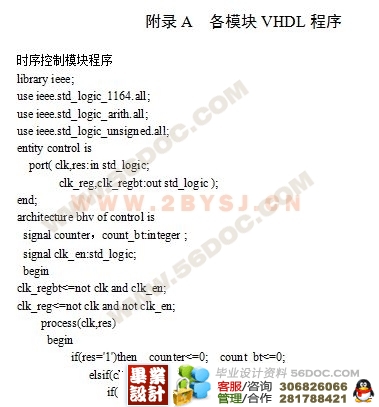

3.1.1 时序控制模块的设计与仿真结果分析 11

3.1.2 延时模块的设计与仿真结果分析 11

(毕业设计)

3.1.3 补码乘加模块的设计与仿真结果分析 12

3.1.4 累加模块的设计与仿真结果分析 13

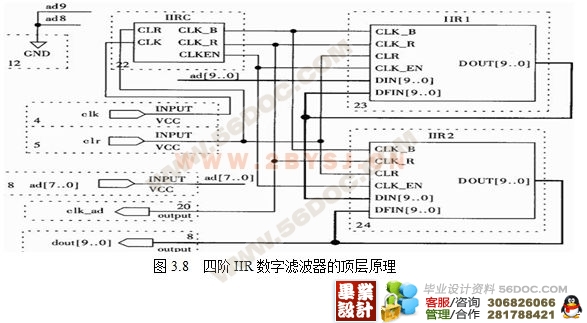

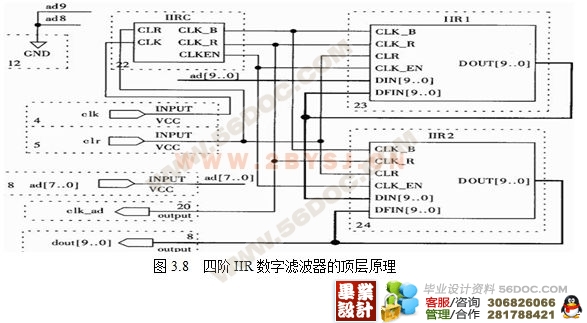

3.1.5 顶层模块设计 14

3.2 IIR数字滤波器的仿真与结果分析 14

3.2.1 IIR数字滤波器的系统设计 14

3.2.2 IIR数字滤波器的系统仿真与结果分析 15

3.2.3 高阶IIR数字滤波器的实现 17

结 论 19

参 考 文 献 20

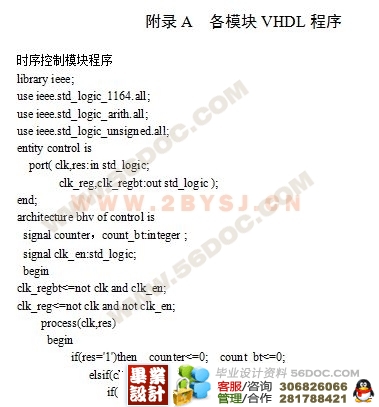

附录A 各模块VHDL程序 21

致 谢 31 |